**Short Paper**

# A Study of a Small-Area and Low-Power Readout Circuit for LOFIC CMOS Image Sensor

Nao Kitajima†, Ai Otani†, Ryotaro Hotta†, Hiroaki Ogawa† and Shunsuke Okura†

Abstract: In a society where a large number of sensors are used, low-cost image sensors with excellent HDR performance are required. To reduce the circuit area, we propose a circuit in which all capacitances are replaced from MIM capacitance to MOS capacitance. As a result, the INL was reduced to a maximum of 7.6 LSB, and the area was reduced by 36.48%.

Keywords: CMOS image sensor, LOFIC, MOS capacitor, small area, double sampling circuit, SAR-ADC

#### 1. Introduction

In the "Trillion Sensors Universe," numerous sensors are expected to be utilized, and the IoT society is expected to progress widely. CMOS image sensors (CIS) are now being used in a wide range of applications, from viewing applications such as digital cameras and smartphones to sensing applications for machines such as autonomous driving and surveillance. CIS used for sensing applications feature HDR (High Dynamic Range), which allows capturing images of objects under extreme lighting conditions such as outdoors.

Up until now, methods to achieve HDR have included logarithmic compression [1], multiple exposure [2], Dual Conversion Gain (DCG) [3], and Lateral Overflow Integration [4].

Capacitor (LOFIC) [3] and other technologies have been proposed.

## CIS with LOFIC pixels has high conversion gain.

In conventional HDR systems, the high-conversion gain (HCG) signal and the low-conversion gain (LCG) signal are combined in a downstream circuit to generate an HDR signal. However, because the HCG signal and the LCG signal have different polarities, two types of readout circuits are required. To address this issue, our research group is studying a single-channel readout circuit [4] that can read out both signals, aiming to reduce the area of the readout circuit.

The HCG signal uses an inverting amplifier circuit to reduce input-equivalent noise, and the LCG signal uses a non-inverting attenuation circuit to enable the readout of highly saturated electrons. Furthermore, by aligning the polarity of the HCG signal and LCG signal through inverting and non-inverting operations, the ADC

Here, most of the readout circuit is occupied by MIM capacitors with low capacitance density.

We are considering using MOS capacitors to further reduce the area of the readout circuit. However, MOS capacitors manufactured using a general manufacturing process are significantly affected by voltage dependency, which causes the output signal to become nonlinear. Therefore, in this paper, we propose a capacitive type capacitor that can fold back the voltage by adjusting the voltage and using an auto-zero circuit with an offset. We propose a small-area readout circuit using MOS capacitors that achieves high linearity through a DAC circuit.

#### 2. Proposed method

#### 2. 1 Circuit configuration

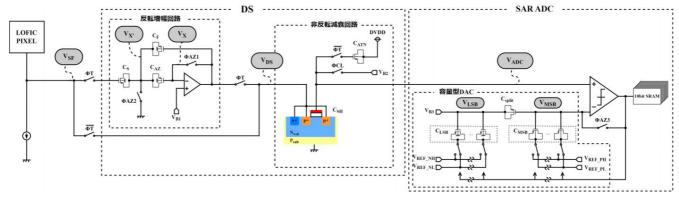

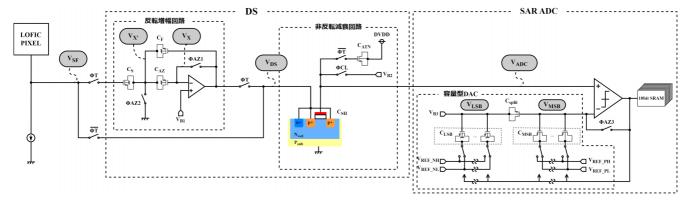

Figure 1 shows a small-area readout circuit using MOS capacitors. The proposed readout circuit is composed of a double sampling (DS) circuit and a successive approximation (SAR) ADC.

Uses MOS capacitors.

The DS circuit is composed of an inverting amplifier circuit that processes the HCG signal using CDS (Correlated Double Sampling) and a non-inverting attenuation circuit that processes the LCG signal using DDS (Differential Double Sampling). The inverting amplifier circuit is configured by adding a ÿAZ2 switch and a CAZ capacitor to the general configuration of a ÿAZ1 switch, two capacitors CS and CF, and an operational amplifier [5]. The non-inverting attenuation circuit is composed of a switch controlled by ÿCL, a sample capacitor CSH, and an attenuation capacitor CATN [6]. Here, the PMOS capacitors CSH and CATN use a device structure in which the back gate is connected to the source and drain terminals. Although a large parasitic capacitance occurs in the NWELL, by connecting the top plate side to the input side of the ADC, the parasitic capacitance is connected to the pixel side with low impedance, so the attenuation rate is small

2024 年 8 月,映像情報メディア学会年次大会で発表 2025 年 1 月 15 日受付,2025 年 3 月 25 日再受付,2025 年 4 月 8 日採録 † 立命館大学 理工学研究科

(〒 525-8577 滋賀県草津市野路東 1 丁目 1-1)

# LOFIC型CMOSイメージセンサに向けた小面積・低消費電力読み出し回路の検討

A Study of a Small-Area and Low-Power Readout Circuit for LOFIC CMOS Image Sensor

Nao Kitajima<sup>†</sup>, Ai Otani<sup>†</sup>, Ryotaro Hotta<sup>†</sup>, Hiroaki Ogawa<sup>†</sup> and Shunsuke Okura<sup>†</sup>

**あらまし** 大量のセンサが使用される社会に向け、低コストで HDR 性能に優れたイメージセンサが求められる. 回路 面積の削減を目的とし、全ての容量を MIM 容量から MOS 容量に置き換えた回路を提案する. その結果、INL は最大 7.6 LSB を示し、面積は 36.48% 低減した.

キーワード: CMOS イメージセンサ, LOFIC, MOS 容量, 小面積, Double Sampling 回路, 逐次比較型 A/D 変換器

# 1. まえがき

"Trillion Sensors Universe"では、多数のセンサが活用され、IoT 社会が広く進展することが期待されている。CMOSイメージセンサ (CIS)は、デジタルカメラやスマートフォンをはじめとするビューイング用途から、自動運転等の機械向けや監視向けといったセンシング用途まで幅広く活用されるようになっている。センシング用途で用いられる CIS は、屋外などの極端な照度条件下で物体を撮像できる HDR (High Dynamic Range)性能が求められる。これまで、HDR を実現する手法として対数圧縮[1]、複数回露光[2]、Dual Conversion Gain (DCG)[3]、Lateral Overflow Integration Capacitor (LOFIC)[3]等が提案されている。

LOFIC 画素を備える CIS では、High Conversion Gain (HCG) 信号と Low Conversion Gain (LCG) 信号を後段 回路にて合成し、HDR 信号を生成する. しかし、HCG 信号と LCG 信号は互いに極性が異なるため、2 種類の読み出し回路を必要とする. この課題に対し、我々の研究グループでは、読み出し回路の小面積化に向けた、両信号を読み出し可能な単チャネル読み出し回路 [4] を検討している. HCG 信号は反転増幅回路を用いて入力換算ノイズを低減し、LCG 信号は非反転減衰回路を用いて高飽和電子の読み出しを可能とする. さらに、反転・非反転動作により HCG 信号と LCG 信号の極性を揃えることで、両信号間で ADC

を共有する。ここで、読み出し回路の大部分は容量密度の低い MIM 容量が占めている。そのため、容量密度の高い MOS 容量を用いて、読み出し回路のさらなる小面積化を検討する。しかし、一般的な製造プロセスを用いた MOS 容量は電圧依存性の影響が大きく、出力信号が非線形となる課題が生じる。そこで、本稿ではオフセット付きオートゼロ回路および電圧調整による電圧折り返し可能な容量型 DAC 回路により、高い線形性を実現する MOS 容量を用いた小面積読み出し回路を提案する。

# 2. 提 案 手 法

# 2.1 回路構成

図 1 に MOS 容量を用いた小面積読み出し回路を示す. 提案する読み出し回路は, Double Sampling (DS) 回路と 逐次比較 (SAR) 型 ADC から構成し,全ての容量素子に MOS 容量を用いる.

DS 回路は HCG 信号を CDS (Correlated Double Sampling) 処理する反転増幅回路と、LCG 信号を DDS (Differential Double Sampling) 処理する非反転減衰回路で構成する。反転増幅回路は、 $\Phi$ AZ1 スイッチ、2 つの容量  $C_S$ ,  $C_F$ , オペアンプといった一般的な構成に、 $\Phi$ AZ2 スイッチと  $C_{AZ}$  容量を追加した構成 [5] とする。非反転減衰回路は、 $\Phi$ CL で制御するスイッチ,サンプル容量  $C_{SH}$ , 減衰容量  $C_{ATN}$  で構成 [6] する。ここで、PMOS 容量  $C_{SH}$ , に大きな寄生容量が生じるものの、トッププレート側を ADC の入力側と接続することで、寄生容量は低インピーダンスの画素側に接続されるため、減衰率

2024 年 8 月,映像情報メディア学会年次大会で発表 2025 年 1 月 15 日受付,2025 年 3 月 25 日再受付,2025 年 4 月 8 日採録 † 立命館大学 理工学研究科

(〒 525-8577 滋賀県草津市野路東 1 丁目 1-1)

The next page is the original paper, which is expanded alternately with the translated version.

Because this is a machine translation, it may contain typographical errors, mistranslations, or parts of the paper that have not been reflected in the translation.

Please be sure to cite the original publication when referencing.

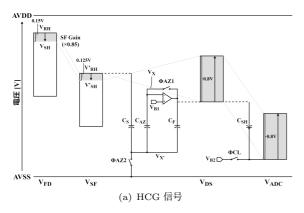

Figure 1 Proposed circuit configuration

In addition, the PMOS capacitor does not require deep well implantation, and by connecting the back gate and source/drain terminals, it can be laid out in a narrow pitch for column-parallel ADCs.

The SAR ADC consists of a comparator, a capacitive DAC, and an SRAM. The capacitive DAC has a split capacitance configuration that can be realized in a small area, and is configured by combining an NMOS capacitor and a PMOS capacitor. In addition, different VREF voltages are applied to the LSB side and the MSB side.

#### 2.2 Operational Overview

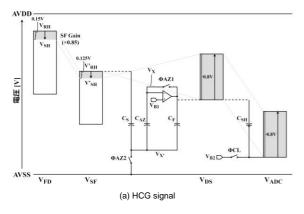

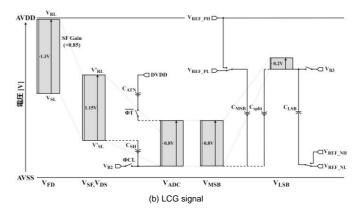

Figure 2 shows a voltage diagram of the HCG signal and LCG signal. When reading out the HCG signal, ÿT is set to HIGH and the signal is read out via an inverting amplifier circuit. On the other hand, when reading out the LCG signal, ÿT is set to LO and the signal is read out via a non-inverting attenuation circuit.

# (1) Inverting amplifier

circuit As shown in Figure 2(a), the HCG signal is first input to the reset signal. The VRH signal, and later the luminance signal VSH, is read out within the pixel (VFD) and output to VSF via the source follower circuit. The NMOS capacitors CS, CF, and CAZ bias the bottom plate (VX) to a low voltage AVSS by turning on ÿAZ1 and ÿAZ2. The top plate (VX) is held at VB1 by virtual grounding. Even after ÿAZ1 and ÿAZ2 are turned off, VX and VX are maintained at VB1 and AVSS, respectively, due to the conservation of charge law. Therefore, the silicon surface of each MOS capacitor is inverted to N-type, and the capacitor operates in the inversion region, where the voltage dependence of the capacitance is small. In conventional inverting amplifier circuits, the voltage difference between both ends is 0 V during auto-zero, making the output signal nonlinear. However, the proposed circuit achieves high linearity by using CAZ. The subsequent operational overview is almost identical to that of the LCG signal, which will be described later.

#### (2) Non-inverting attenuation

circuit As shown on the left in Figure 2 (b), the LCG signal is first read out as the luminance signal VSL and then as the reset signal VRL in the pixel (VFD), and then output to VSF via the source follower circuit. When resetting the attenuation capacitance by turning on ÿCL, the top plate side of the PMOS capacitance CSH is biased to a low voltage VB2 to maintain the luminance VSL signal. Here, the minimum value of V and the comparator input

Considering the input voltage VB2 , the voltage difference between both ends of CSH is small compared to other MOS capacitors, so the back gate is connected to the source-drain terminal to prevent the rise in threshold voltage due to the substrate bias effect. The PMOS capacitor CATN operates in the inversion region because the bottom plate side is biased to a high voltage DVDD . Here, by using DVDD as the bias voltage instead of AVDD , the voltage difference between both ends of the capacitor is brought closer to CSH , and the nonlinearity of the capacitance value that occurs when reading out high-brightness signals is compensated for. However , in order to reduce digital noise interference via DVDD, the DS circuit and the digital circuit must be laid out with

separate wiring. (3) Capacitive DAC circuit

The linearity of the capacitive DAC is improved by folding back the voltage using PMOS capacitance for CMSB and Csplit and NMOS capacitance for CLSB. As shown on the right of Figure 2 (b), the PMOS capacitance group on the MSB side In the CMSB, the top plate voltage is virtually grounded to VB2 when auto-zero is enabled, so the bottom plate VREF voltage (VREF PH, By setting VREF (PL) at a high voltage, it operates in the inversion region. Similarly, the PMOS split capacitance Csplit is (VLSB node) is reset with a high voltage VB3.

The NMOS capacitance group CLSB operates in the inversion region by\_ setting the VREF voltage (VREF NH, VREF NL) to a low voltage and folding back the operating voltage for CMSB and Csplit . In

addition, in a split capacitance type DAC , the VREF voltages on the LSB side and MSB side are made independent to correct A/D conversion errors. By adjusting the VREF amplitude on the MSB side (VREF PH-VREF PL) , A/D conversion gain errors due to the parasitic capacitance of the VMSB node, etc. are corrected. The VREF amplitude on the LSB side (VREF NH-By adjusting the VREF (NL) , the DNL error caused by the parasitic capacitance of the VLSB node is corrected.

# 3. Verification results

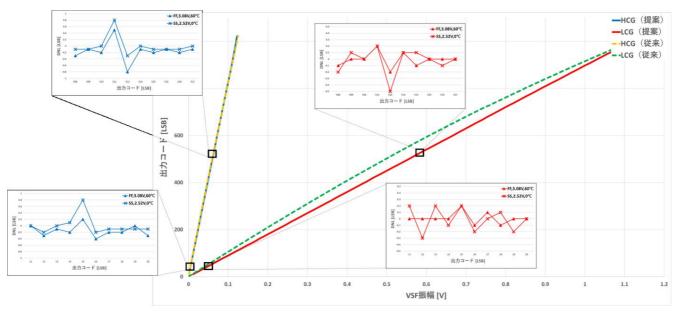

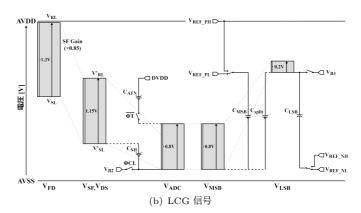

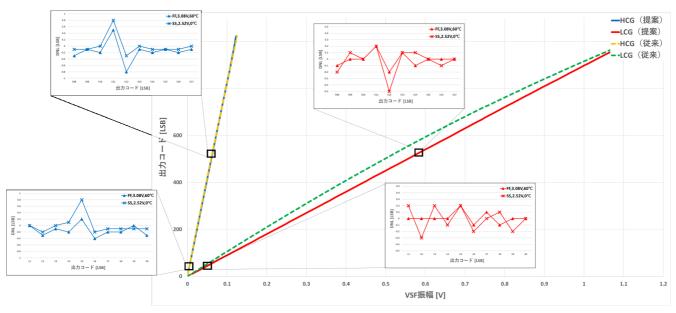

The proposed readout circuit (10- bit resolution) was designed using a 0.18 ÿm CMOS process, and SPICE simulations were performed under corner conditions (transistors: Slow, Typical, Fast, power supply voltage: 2.52 V, 2.8 V, 3.08 V, operating temperature: 0 °C, 25 °C, 60 °C) . Figure 3 shows the A/D conversion efficiency versus the amplitude of the pixel signal output VSF .

[Copyrights to Machine TranslatedContent]

図 1 提案回路構成

に影響しない。また、PMOS 容量は深いウェル注入を必要とせず、バックゲートとソース・ドレイン端子を接続することで列並列 ADC の狭いピッチにレイアウトすることができる。

SAR 型 ADC はコンパレータ,容量型 DAC,SRAM で構成する.容量型 DAC は,小面積で実現可能なスプリット容量構成とし,NMOS 容量と PMOS 容量を組み合わせて構成する.また,LSB 側と MSB 側に異なる  $V_{REF}$  電圧を印加する.

#### 2.2 動作概要

図 2 に HCG 信号と LCG 信号における電圧概略図を示す。HCG 信号を読み出す場合, $\Phi T$  を HIGH 動作させることで反転増幅回路を経由して読み出しを行う。一方,LCG 信号を読み出す場合, $\Phi T$  を LO 動作させることで非反転減衰回路を経由して読み出しを行う。

# (1) 反転增幅回路

図 2 (a) に示すように、HCG 信号は先にリセット信号  $V_{RH}$ ,後に輝度信号  $V_{SH}$  が画素内 ( $V_{FD}$ ) にて読み出され,ソースフォロア回路を介して  $V_{SF}$  に出力される.NMOS 容量  $C_S$ ,  $C_F$ ,  $C_{AZ}$  は, $\Phi AZ1$  および  $\Phi AZ2$  をオンすることでボトムプレート側( $V_{X'}$ )を低い電圧 AVSS にバイアスする.トッププレート側( $V_X$ )は仮想接地により  $V_{B1}$  が保持される. $\Phi AZ1$  および  $\Phi AZ2$  をオフした後も,電荷保存則により  $V_X$  および  $V_{X'}$  はそれぞれ  $V_{B1}$  および AVSSに保たれる.従って,各 MOS 容量はシリコン表面が N 型に反転し,容量の電圧依存性が小さい反転領域で動作する.従来の反転増幅回路ではオートゼロ時の両端電位差が 0 V となり,出力信号が非線形となるのに対して,提案回路では  $C_{AZ}$  を用いることで高い線形性を実現する.以降の動作概要は,後述する LCG 信号とほぼ同一となる.

# (2) 非反転減衰回路

図 2 (b) 左に示すように、LCG 信号は先に輝度信号  $V_{SL}$ 、後にリセット信号  $V_{RL}$  が画素内 ( $V_{FD}$ ) にて読み出され、ソースフォロア回路を介して  $V_{SF}$  に出力される。 $\Phi CL$  をオンする減衰容量のリセット時には、PMOS 容量  $C_{SH}$  のトッププレート側を低い電圧  $V_{B2}$  にバイアスして輝度信号  $V_{SL}$  を保持する。ここで、 $V_{SL}$  の最小値とコンパレータ入

力電圧  $V_{B2}$  を考慮すると、 $C_{SH}$  の両端電位差が他の MOS 容量に対して小さいため、バックゲートをソース・ドレイン端子と接続し、基板バイアス効果による閾値電圧の上昇を抑止する。 PMOS 容量  $C_{ATN}$  は、ボトムプレート側を高い電圧 DVDD にバイアスするため、反転領域で動作する。 ここで、バイアス電圧を AVDD ではなく、DVDD とすることで容量の両端電位差を  $C_{SH}$  に近づけ、高輝度信号読み出し時に生じる容量値の非線形性を補完する。 ただし、DVDD を経由したデジタルノイズ干渉を低減するため、DS 回路とデジタル回路は配線をレイアウト分離する必要がある。

# (3) 容量型 DAC 回路

$C_{MSB}$  と  $C_{split}$  に PMOS 容量, $C_{LSB}$  に NMOS 容量を用いて電圧を折り返すことで,容量型 DAC の線形性を向上する.図 2 (b) 右に示すように,MSB 側の PMOS 容量群  $C_{MSB}$  は,トッププレート側電圧がオートゼロ時に  $V_{B2}$  に仮想接地するため,ボトムプレート側  $V_{REF}$  電圧 ( $V_{REF,PH}$ ,  $V_{REF,PL}$ ) を高い電圧とすることで,反転領域で動作する.同様に PMOS スプリット容量  $C_{split}$  は,ボトムプレート側 ( $V_{LSB}$  ノード) を高い電圧  $V_{B3}$  でリセットする.LSB 側の NMOS 容量群  $C_{LSB}$  は, $V_{REF}$  電圧 ( $V_{REF,NH}$ ,  $V_{REF,NL}$ ) を低い電圧として, $C_{MSB}$  および  $C_{split}$  に対して動作電圧を折り返すことで,反転領域で動作する.

また、スプリット容量型 DAC では、LSB 側と MSB 側の  $V_{REF}$  電圧を独立にすることで、A/D 変換の誤差を補正する.MSB 側の  $V_{REF}$  振幅  $(V_{REF\_PH}-V_{REF\_PL})$  を調整することで、 $V_{MSB}$  ノードの寄生容量等による A/D 変換利得誤差を補正する.LSB 側の  $V_{REF}$  振幅  $(V_{REF\_NH}-V_{REF\_NL})$  を調整することで、 $V_{LSB}$  ノードの寄生容量等による DNL 誤差を補正する.

# 3. 検証 結果

提案する読み出し回路 (10 bit 分解能) を  $0.18~\mu m$  CMOS プロセスで設計し、コーナー条件(トランジスタ: Slow、Typical、Fast、電源電圧: 2.52 V, 2.8 V, 3.08 V, 動作温度: 0 °C, 25 °C, 60 °C) で SPICE シミュレーションを行った.図 3 は画素信号出力  $V_{SF}$  の振幅に対する A/D

Because this is a machine translation, it may contain typographical errors, mistranslations, or parts of the paper that have not been reflected in the translation.

Please be sure to cite the original publication when referencing.

Figure 2. Voltage schematic diagram

Figure 3. A/D conversion characteristics

Table 1. Layout area comparison (width 11.2 ÿm) Conventional

|   |            | circuit (MIM capacitor) Proposed circu | it (MOS capacitor) |

|---|------------|----------------------------------------|--------------------|

|   | DS circuit | 577.25 ÿm                              | 172.95 ÿm          |

| 3 | SAR-ADC    | 1108.48 ÿm                             | 897.71 ÿm          |

The conversion characteristics are shown below. For the HCG signal, the INL was +11.2/-5.0 LSB for the conventional circuit using MOS capacitors and +7.1/-4.9 LSB for the proposed circuit . For the LCG signal, the INL was +39.3/-21.4 LSB for the conventional circuit and +7.6/-2.5 LSB for the proposed circuit . The INL , which is an issue even when using MOS capacitors, was compared with the ideal output.

We confirmed that good results of less than 1% were achieved. Furthermore, the DNL of the proposed circuit was +0.8/-0.8 LSB for the HCG signal and +0.2/-0.5 LSB for the LCG signal, confirming that the DNL error could be corrected without code jumps. The DS circuit and SAR -type ADC were laid out in parallel with an 11.2 ÿm pitch. As shown in Table 1, the area of the proposed circuit using MOS capacitors was reduced by 36.48% compared to the conventional circuit using MIM capacitors in the readout circuit.

# 4. Conclusion

We proposed a readout circuit for LOFIC -type CIS using high-density MOS capacitors. Simulation results confirmed high linearity with an INL of +7.6/-4.9 LSB for the input/output characteristics of HCG and LCG signals. Layout results also confirmed a 36.48% reduction in area. Acknowledgments: This research was conducted in cooperation with Cadence Design Systems Japan, Inc. and Synopsys Japan, LLC through the University of Tokyo VDEC activities.

[文献]

- D. Scheffer, B. Dierickx and G. Meynants: "Random addressable 2048/spl times/2048 active pixel image sensor", IEEE, 44, 10, pp. 1716-1720 (1997)

- H. Komobuchi, A. Fukumoto, T. Yamada, Y. Matsuda and T. Kuroda: "1/4 inch ntsc format hyper-d range il-ccd", Proc. 1995 IEEE Workshop on CCDs and AISs. SS-1, Apr. (1995)

- N. Akahane, S. Sugawa, S. Adachi, K. Mori, T. Ishiuchi and K. Mizoubuchi: "A sensitivity and linearity improvement of a 100-db dynamic range cmos image sensor using a lateral overflow integration capacitor", IEEE, 41, 4, pp. 851–858 (2006)

- 4) A. Otani, H. Ogawa, K. Miyauchi, S. Han, H. Owada, I. Takayanagi and S. Okura: "An area-efficient up/down double-

図 2 電圧概略図

図 3 A/D 変換特性

表 1 レイアウト面積比較(幅 11.2 μm)

|         | 従来回路(MIM 容量)         | 提案回路(MOS 容量)        |

|---------|----------------------|---------------------|

| DS 回路   | $577.25~\mu{\rm m}$  | $172.95~\mu{\rm m}$ |

| SAR-ADC | $1108.48~\mu{\rm m}$ | 897.71 $\mu m$      |

変換特性を示す。INL について HCG 信号の場合,MOS 容量を用いた従来回路は +11.2/-5.0 LSB,提案回路は +7.1/-4.9 LSB であった。LCG 信号の場合,従来回路は +39.3/-21.4 LSB,提案回路は +7.6/-2.5 LSB であった。MOS 容量を用いても課題となる INL は理想出力と比較して 1% 以下と良好な結果になることを確認した。さらに,提案回路の DNL について,HCG 信号は +0.8/-0.8 LSB,LCG 信号は +0.2/-0.5 LSB とコード飛びすることなく DNL 誤差を補正できることを確認した。また,DS 回路と SAR 型 ADC を  $11.2~\mu$ m ピッチで並列にレイアウトした。表 1 に示すように,読み出し回路に MIM 容量を用いた従来回路に対して,MOS 容量を用いた提案回路は面積が 36.48% 低減した。

## 4. む す び

容量密度の高い MOS 容量を用いた LOFIC 型 CIS 向けの読み出し回路を提案した。シミュレーション結果より,HCG 信号と LCG 信号における入出力特性は,INLが +7.6/-4.9 LSB と高い線形性を確認した。また,レイアウト結果から面積を 36.48 % 低減することを確認した。謝辞:本研究は,東京大学 VDEC 活動を通して,日本ケイデンス・デザイン・システムズ社,日本シノプシス合同会社の協力で行われたものである。

# 〔文献〕

- D. Scheffer, B. Dierickx and G. Meynants: "Random addressable 2048/spl times/2048 active pixel image sensor", IEEE, 44, 10, pp. 1716–1720 (1997)

- H. Komobuchi, A. Fukumoto, T. Yamada, Y. Matsuda and T. Kuroda: "1/4 inch ntsc format hyper-d range il-ccd", Proc. 1995 IEEE Workshop on CCDs and AISs. SS-1, Apr. (1995)

- N. Akahane, S. Sugawa, S. Adachi, K. Mori, T. Ishiuchi and K. Mizoubuchi: "A sensitivity and linearity improvement of a 100-db dynamic range cmos image sensor using a lateral overflow integration capacitor", IEEE, 41, 4, pp. 851–858 (2006)

- A. Otani, H. Ogawa, K. Miyauchi, S. Han, H. Owada, I. Takayanagi and S. Okura: "An area-efficient up/down double-

The next page is the original paper, which is expanded alternately with the translated version.

Because this is a machine translation, it may contain typographical errors, mistranslations, or parts of the paper that have not been reflected in the translation.

Please be sure to cite the original publication when referencing.

- sampling circuit for a lofic cmos image sensor", Sensors, **23**, 9, p. 4478 (2023)

- R. Hotta, S. Okura, A. Otani, K. Tatsuta, K. Miyauchi, S. Han, H. Owada and I. Takayanagi: "A small-area and highly-linear column readout circuit for lofic cmos image sensor", IST, 47, 22, pp. 7–12 (2023)

- N. Kitajima, A. Otani, R. Hotta and S. Okura: "A study of a small-area and low-power readout circuit for lofic cmos image sensor (1)", ITE Annual Convention(2024)

また。 をき 直 2024 年,立命館大学理工学部電子情 本工学科卒業・現在は、同大学大学院理工学研究科電子システム専攻博士課程前期課程に在籍、イメージセンサのアナログ回路に関する研究に従事.

大会 変 2021 年,立命館大学理工学部電子情報工学科卒業 2023 年,同大学大学院理工学研究科電子システム専攻博士課程前期課程修了.現在は,同大学院理工学研究科電子システム専攻博士課程後期課程に在籍.イメージセンサに関する研究に従事.

ほったりょう た 35 堀田 彦 太 郎 2023 年,立命館大学理工学部電子情報工学科卒業。2025 年,同大学大学院理工学研究科電子システム専攻博士課程前期課程修了。イメージセンサのアナログ回路に関する研究に従事。

大会 (女人) 1 (1945年) 大学 (女人) 2003年,大阪大学卒業. 2005年,同大学院博士前期課程修了. 2010年,同大学院博士(工学)を取得. 2007年より株式会社 Rosnes, 2010年よりルネサスエレクトロニクス株式会社、2014年よりブリルニクスジャパン株式会社を経て,CMOSイメージセンサの研究開発に従事. 2019年より立命館大学理工学部電子情報工学科 准教授. 2024年より同大学 教授. CMOSイメージセンサの画素デバイスや周辺回路,ハードウェアセキュリティ,画像認識,IoTへの応用などの研究に従事. 正会員.

- sampling circuit for a lofic cmos image sensor", Sensors, 23, 9, p. 4478 (2023)

- R. Hotta, S. Okura, A. Otani, K. Tatsuta, K. Miyauchi, S. Han, H. Owada and I. Takayanagi: "A small-area and highly-linear column readout circuit for lofic cmos image sensor", IST, 47, 22, pp. 7–12 (2023)

- N. Kitajima, A. Otani, R. Hotta and S. Okura: "A study of a small-area and low-power readout circuit for lofic cmos image sensor (1)", ITE Annual Convention(2024)

\*たじま 恒 2024 年, 立命館大学理工学部電子情報工学科卒業. 現在は, 同大学大学院理工学研究科電子システム専攻博士課程前期課程に在籍. イメージセンサのアナログ回路に関する研究に従事.

またに 大会 変 2021 年,立命館大学理工学部電子情報工学科卒業 2023 年,同大学大学院理工学研究科電子システム専攻博士課程前期課程修了.現在は,同大学院理工学研究科電子システム専攻博士課程後期課程に在籍.イメージセンサに関する研究に従事.

ほった 9よう 太 8 2023 年, 立命館大学理工学部電子情報 田遼太郎 2023 年, 立命館大学理工学部電子情報工学科卒業。2025 年, 同大学大学院理工学研究科電子システム専攻博士課程前期課程修了。イメージセンサのアナログ回路に関する研究に従事。

大倉 (教介) 2003年,大阪大学卒業. 2005年,同大学院博士前期課程修了. 2010年,同大学院博士(工学)を取得. 2007年より株式会社 Rosnes, 2010年よりルネサスエレクトロニクス株式会社、2014年よりブリルニクスジャパン株式会社を経て,CMOSイメージセンサの研究開発に従事. 2019年より立命館大学理工学部電子情報工学科 准教授. 2024年より同大学 教授. CMOSイメージセンサの画素デバイスや周辺回路,ハードウェアセキュリティ,画像認識,IoTへの応用などの研究に従事. 正会員.