Short paper

# A Variable-Resolution Single-Slope ADC for Feature Extractable **CMOS Image Sensor**

Itsuki Matsubara†, Ryuichi Ujiie††, Daisuke Morikawa††, Hideki Shima†† and Shunsuke Okura†

Abstract: We investigated an A/D converter for a CMOS image sensor capable of outputting features to improve the energy efficiency of image recognition systems . Simulation results showed that the current consumption in feature extraction mode could be reduced by 87.83% compared to image capture mode.

Keywords: CMOS image sensor, A/D converter, Low power consumption, Image recognition

# 1. Introduction

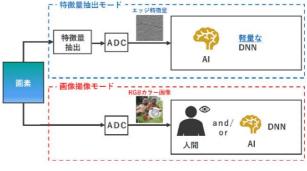

In the Trillion Sensors Universe [1], a society in which one trillion sensors are used annually, with 125 sensors per person, a huge amount of information is collected. Al -based recognition is therefore expected to be applied to image information. However, images captured by conventional CMOS image sensors contain a lot of redundant data, which is thought to increase the overall system power consumption and latency. Therefore, our research group has proposed using edge features that eliminate redundant data for Al-based image recognition, thereby reducing the overall system power consumption [2]. Figure 1 shows an overview of the proposed event-detection image recognition system. Normally, edge features with low information content are output for AI recognition, and image recognition is performed using a lightweight DNN (Deep Neural Network) (feature extraction mode). When an event is detected, an RGB color image is output, and image recognition is performed by the human eye or a general DNN (image capture mode).

In previous research [3] , we developed a SAR sensor that can output both RGB color images and edge features .

The bit resolution is variable using a successive approximation register (SAR) type A/D converter, and power consumption is significantly reduced by lowering the resolution during feature extraction. 2.1 Overall circuit configuration

The SAR type A/D converter has a large circuit area, so chip costs are high.

2024年8月、映像情報メディア学会年次大会で発表 2025年1月14日受付, 2025年3月12日再受付, 2024年5月9日採録

(〒 525-8577 滋賀県草津市野路東 1 丁目 1-1) ††日清紡マイクロデバイス株式会社 (〒 103-8456 東京都中央区日本橋横山町 3 番 10 号)

On the other hand, single-slope A/D converters are suitable for reducing the area, but because they consume a constant current, the power consumption cannot be significantly reduced even if the bit resolution is reduced. To solve this problem, this paper proposes a single-slope A/D converter that can reduce power consumption in feature extraction mode for CMOS image sensors capable of outputting features.

# 2. Proposed single-slope A/D converter

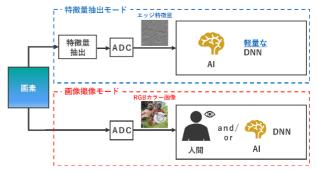

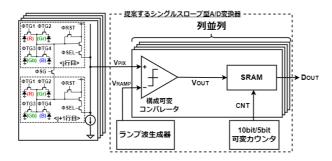

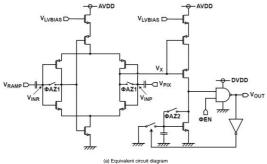

Figure 2 shows the overall circuit configuration of the proposed columnparallel single-slope A/D converter. The pixels are assumed to be Bayer array

4- pixel shared type. The proposed circuit consists of a configurable comparator, SRAM, a bit-number variable counter, and a ramp wave generator. The pixel signal VPIX and the ramp signal VRAMP are compared by the comparator, and the counter value is stored in the SRAM when the signal voltages become equal.

# 特徴量出力可能な CMOS イメージセンサに向けた可変分解 能シングルスロープ型 A/D 変換器の検討

A Variable-Resolution Single-Slope ADC for Feature Extractable CMOS Image Sensor

Itsuki Matsubara<sup>†</sup>, Ryuichi Ujiie<sup>††</sup>, Daisuke Morikawa<sup>††</sup>, Hideki Shima<sup>††</sup> and Shunsuke Okura<sup>†</sup>

**あらまし** 画像認識システムのエネルギー効率を向上させる特徴量出力可能な CMOS イメージセンサに向けた A/D 変換器を検討した. シミュレーションの結果,特徴量抽出モード時の消費電流量が画像撮像モード時と比較して 87.83% 削減できることが分かった.

キーワード: CMOS イメージセンサ, A/D 変換器, 低消費電力, 画像認識

# 1. まえがき

年間1兆個,1人あたり125個ものセンサを使用する社 会, Trillion Sensors Universe [1] では膨大な情報が収集 されるため、画像情報に向けて AI による認識が期待され ている.しかし,画像認識において従来の CMOS イメー ジセンサの撮像画像では冗長なデータが多く含まれており, システム全体の消費電力や遅延の増大につながると考えら れる. そこで、我々の研究グループでは、AIによる画像認 識には冗長なデータを省いたエッジ特徴量を用い、システ ム全体の消費電力を削減することを提案している [2]. 図1 に、提案しているイベント検知型画像認識システムの概要 を示す. 通常は、AIが認識するために情報量の少ないエッ ジ特徴量を出力し、軽量な DNN (Deep Neural Network) による画像認識を行う(特徴量抽出モード). イベント検知 をすると、RGB カラー画像を出力し、人間の目による認 識や一般的な DNN による画像認識を行う(画像撮像モー ド). 先行研究 [3] では、RGB カラー画像とエッジ特徴量の 両方を出力可能な CMOS イメージセンサに向けて、SAR (Successive Approximation Register) 型 A/D 変換器を 用いてビット分解能を可変とし、特徴量抽出時においては 分解能を下げることで消費電力を大幅に低減した. しかし, SAR型A/D変換器は回路面積が大きいため、チップコス

図 1 イベント検知型画像認識システムの概要(人物画像 [4,5])

トが高くなってしまう.一方,シングルスロープ型 A/D 変換器は小面積化には適しているが,定常電流を消費するため,ビット分解能を下げても消費電力を大幅に低減できないことが課題となる.本稿ではこの課題を解決するために,特徴量出力可能な CMOS イメージセンサに向けて,特徴量抽出モードにおける消費電力を低減可能なシングルスロープ型 A/D 変換器を提案する.

#### 2. 提案するシングルスロープ型 A/D 変換器

# 2.1 全体回路構成

図 2 に提案する列並列シングルスロープ型 A/D 変換器の全体回路構成を示す。画素はベイヤー配列 4 画素共有型を想定している。提案回路は構成可変コンパレータと SRAM, ビット数可変カウンタ,ランプ波生成器から構成する。画素信号  $V_{PIX}$  とランプ信号  $V_{RAMP}$  をコンパレータで比較し,信号電圧が等しくなるタイミングでカウンタの値を SRAM

<sup>2024</sup> 年 8 月,映像情報メディア学会年次大会で発表 2025 年 1 月 14 日受付,2025 年 3 月 12 日再受付,2024 年 5 月 9 日採録

<sup>†</sup>立命館大学 理工学研究科 (〒 525–8577 滋賀県草津市野路東 1 丁目 1–1)

<sup>††</sup> 日清紡マイクロデバイス株式会社

<sup>(〒 103-8456</sup> 東京都中央区日本橋横山町 3 番 10 号)

Because this is a machine translation, it may contain typographical errors, mistranslations, or parts of the paper that have not been reflected in the translation.

Please be sure to cite the original publication when referencing.

Figure 2. Overall circuit configuration of the proposed column-parallel single-slope A/ D converter

Figure 3. Circuit diagram of the variable configuration comparator

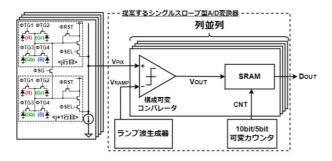

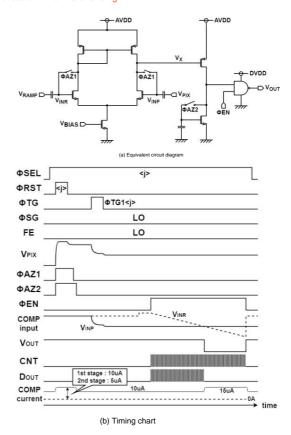

A/D conversion is performed at 10-bit resolution in image capture mode and at 5-bit resolution in feature extraction mode . 2.2 Configurable Comparator Figure 3 shows the circuit diagram of the

configurable comparator.

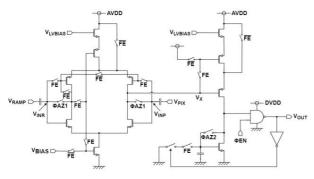

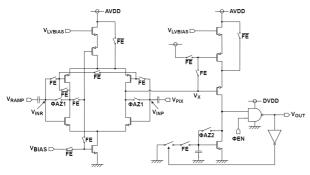

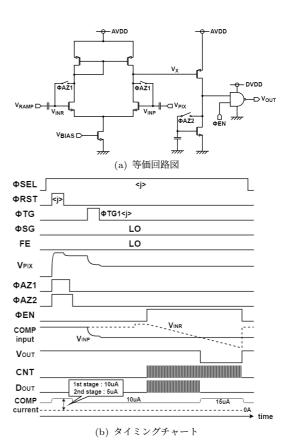

The comparator switches its circuit configuration using the control signal FE . Figure 4 shows the equivalent circuit diagram and timing chart of the reconfigurable comparator in image capture mode (FE = Low) . The counter frequency is 40 MHz . The first stage of the comparator is a differential amplifier circuit using a constant current source, and the second stage is a double-clamped source-grounded circuit [6] , and it operates as a high-precision comparator. Figure 5 shows the equivalent circuit diagram and timing chart of the reconfigurable comparator in feature extraction mode (FE = High).

The timing chart is shown below. When transferring pixel signals, TG1 to TG4 are turned on simultaneously to read out the Bayer array pixel cell signals, and the Bayer array pixel cell signals are converted into pseudo-luminance signals [2]. In addition, the ramp signal is raised by 0.5Vref before the comparison operation so that the output code when the luminance difference between the vertically adjacent pixel cells is 0V becomes the center code. Here, Vref is the A/D conversion reference voltage. The counter frequency is set to 1.25MHz to ease timing constraints. The first stage of the comparator is a Complementary Self-biased Differential Amplifier (CSDA) [7], and the second stage is a double-clamped source-grounded circuit with added feedback control. CSDA

Although the second stage consumes current only during auto-zero and output inversion, the peak current depends on the power supply voltage. Therefore, an NMOS transistor with the bias voltage VLVBIAS as the gate voltage is used, and VLVBIAS - VGS is used as a pseudo power supply voltage to limit the current amount. In addition, to stop the constant current that flows when the input voltage VX of the second stage drops below the inversion voltage, an output

Figure 4. Configurable comparator in image capture mode

When the voltage VOUT inverts, the constant current is turned off by feedback control. Because the edge feature is the brightness difference between adjacent pixels above and below, the signal fluctuates positively or negatively depending on the scene.

Therefore, CSDA, whose input common-mode voltage range extends above and below the operating point, is suitable for signals obtained in feature extraction mode.

#### 3. Simulation Results

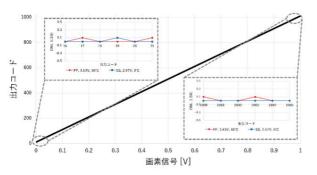

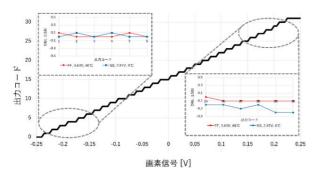

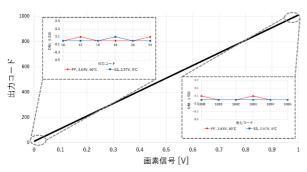

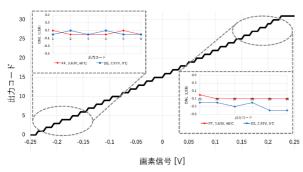

The proposed single-slope A/D converter was designed using a 0.18  $\bar{y}m$  process. SPICE simulations were performed under corner conditions: transistors in slow, normal, and fast modes; analog power supply voltages AVDD of 2.97 V, 3.3 V, and 3.63 V; and operating temperatures of 0 °C, 25 °C, and 60 °C. Figure 6 shows the A/D conversion characteristics in image capture mode, where the DNL was +0.1/-0.0 LSB and the INL was +2.5/-1.3 LSB for 10-bit resolution. Figure 7 shows the A/D conversion characteristics in feature extraction mode, where the DNL was +0.1/-0.4 LSB and the INL was +0.8/-0.6 LSB for 5-bit resolution. Table 1 summarizes the simulation results for DNL, INL, and current consumption. The results confirmed that by configuring the comparator with a variable configuration and operating at low power in feature extraction mode, the current consumption of the comparator in feature extraction mode was reduced to 1.82  $\bar{y}A$ , a reduction of 87.83% from 14.96  $\bar{y}A$  in image capture mode.

#### 4. Conclusion

In this paper, we present a method for detecting a CMOS image sensor capable of outputting feature quantities.

図 2 提案する列並列シングルスロープ型 A/D 変換器の全体 回路構成

図3 構成可変コンパレータの回路図

に保持する. 画像撮像モード時は 10-bit 分解能, 特徴量抽 出モード時は 5-bit 分解能で A/D 変換を行う.

#### 2.2 構成可変コンパレータ

図3 に構成可変コンパレータの回路図を示す. 構成可変 コンパレータは制御信号 FE によって回路構成を切り替え る. 図 4 に画像撮像モード時 (FE=Low) における構成可 変コンパレータの等価回路図およびタイミングチャートを 示す. カウンタ周波数は 40MHz とする. コンパレータ 1 段目が定電流源を用いた差動増幅回路,2段目がダブルクラ ンプ型ソース接地回路 [6] となり、高精度のコンパレータ として動作する. 図 5 に特徴量抽出モード時(FE=High) における構成可変コンパレータの等価回路図およびタイミ ングチャートを示す. 画素信号転送時には TG1~4 を同時 にオンして読み出し、ベイヤー配列画素セル信号を疑似的 な輝度信号に変換する[2].また、上下に隣接する画素セル の輝度差分が OV となるときの出力コードが中心コードと なるように、比較動作前にランプ信号を $0.5V_{ref}$ 持ち上げ る. ここで、 $V_{ref}$  は A/D 変換参照電圧である. カウンタ 周波数は 1.25MHz とすることで、タイミング制約を緩和 する. コンパレータ 1 段目が Complementary Self-biased Differential Amplifier (CSDA) [7], 2 段目が帰還制御を 追加したダブルクランプ型ソース接地回路となる. CSDA は、オートゼロ時および出力反転時しか電流を消費しない ものの、ピーク電流が電源電圧に依存するため、バイアス 電圧  $V_{LVBIAS}$  をゲート電圧とする NMOS トランジスタを 用い、V<sub>LVBIAS</sub> – V<sub>GS</sub> を疑似的な電源電圧として、電流量 を制限する. また、2段目の入力電圧  $V_X$  が反転電圧より 低下することによって流れる定電流を止めるために,出力

図 4 画像撮像モードにおける構成可変コンパレータ

電圧  $V_{OUT}$  が反転すると、帰還制御により定電流をオフする. エッジ特徴量は上下に隣接する画素の輝度差分であるため、シーンに応じて信号は正または負に変動する. よって、入力同相電圧範囲が動作点から上下に広がる CSDA は、特徴量抽出モード時に得られる信号に適している.

# 3. シミュレーション結果

提案したシングルスロープ型 A/D 変換器を  $0.18\mu m$  プロセスを用いて設計し、トランジスタは Slow、Normal、Fast、アナログ電源電圧 AVDD は 2.97V、3.3V、3.63V、動作温度は 0 °C、25 °C、60 °Cのコーナー条件で SPICE シミュレーションを行った。 図 6 は画像撮像モード時の A/D 変換特性を示しており、10-bit 分解能に対して、DNL は+0.1/-0.0 LSB、INL は+2.5/-1.3 LSB となった。 図 7 は特徴量抽出モード時の A/D 変換特性を示しており、5-bit 分解能に対して、DNL は+0.1/-0.4 LSB、INL は+0.8/-0.6 LSB となった。 DNL、INL、消費電流についてのシミュレーション結果を表 1 にまとめる。結果より、コンパレータを可変構成にし、特徴量抽出モード時に低電力動作をすることによって、特徴量抽出モード時のコンパレータの消費電流は  $1.82\mu A$  と、画像撮像モード時の  $14.96\mu A$  から 87.83%削減可能なことを確認した。

#### 4. む す び

本稿では、特徴量出力可能な CMOS イメージセンサに用

Because this is a machine translation, it may contain typographical errors, mistranslations, or parts of the paper that have not been reflected in the translation.

Please be sure to cite the original publication when referencing.

Figure 5. Configurable comparator in feature extraction mode

Figure 6. A/D conversion characteristics in image capture mode (10-bit)

Figure 7. A/D conversion characteristics in feature extraction mode (5-bit)

In the feature extraction mode, the configurable comparator is configured with a CSDA equipped with a peak current limiting circuit and a source-grounded circuit using feedback control, which allows for the image capture to be performed smoothly.

Table 1 Simulation results Image capture

|      | 画像撮像モード         | 特徴量抽出モード        |

|------|-----------------|-----------------|

| 分解能  | 10-bit          | 5-bit           |

| DNL  | +0.1/-0.0 [LSB] | +0.1/-0.4 [LSB] |

| INL  | +2.5/-1.3 [LSB] | +0.8/-0.6 [LSB] |

| 消費電流 | 14.96 [μA]      | 1.82 [μA]       |

Using SPICE simulation, we confirmed that a reduction of 87.83% was possible compared to the imaging mode. In the future, we plan to prototype the proposed circuit and conduct measurement evaluations.

Acknowledgments This research was conducted in cooperation with Cadence Design Systems Japan and Synopsys Japan, Ltd. through the VDEC activities of the University of Tokyo.

#### [文献]

- 1) 神永晉, 金尾寛人: "トリリオン・センサのもたらす変革: 研究開発から 1 産業創出へ (<特集>トリリオンセンサユニバースにおけるシステム制御情 報技術)", システム/制御/情報, **59**, 11, pp. 400-405 (2015).

- Y. Morikaku, R. Ujiie, D. Morikawa, H. Shima, K. Yoshida and S. Okura: "On-Chip Data Reduction and Object Detection for a Feature-Extractable CMOS Image Sensor", Electronics, 13, 21 (2024).

- K. Itsuki, A. Otani, H. Ogawa and S. Okura: "A Variable-Resolution SAR ADC with 10-bit Image Capturing Mode and 5-bit Feature Extraction Mode", ITE Technical Report, 46, 41, pp. 43–44 (2022).

- K. Kuroda, Y. Morikaku, Y. Osuka, R. Iegaki, K. Yoshida and S. Okura: "Lightweight Object Detection Model for a CMOS Image Sensor with Binary Feature Extraction", 2024 IEEE SENSORS (2024).

- T. Lin, M. Maire, S. Belongie, J. Hays, P. Perona, D. Ramanan,

P. Dollár and C. Zintnick: "Microsoft COCO: Common Objects in Context", Computer Vision – ECCV 2024, pp. 740–755 (2014).

- 6) S. Sukegawa, T. Umebayashi, T. Nakajima, H. Kawanobe, K. Koseki, I. Hirota, T. Haruta, M. Kasai, K. Fukumoto, T. Wakano, K. Inoue, H. Takahashi, T. Nagano, Y. Nitta and N. Fukushima: "A 1/4 inch 8Mpixel Back-Illuminated Stacked CMOS Image Sensor", 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, pp. 484–485 (2013).

- M. Bazes: "Two Novel Fully Complementary Self-Biased CMOS Differential Amplifiers", IEEE Journal of Solid-State Circuits, 26, 2, pp. 165–168 (1991).

まつばら いっき 松原 一樹 2024年,立命館大学理工学部電子情報工学科卒業.現在は,同大学大学院理工学研究科電子システム専攻博士課程前期課程に在籍.イメージセンサの A/D 変換器に関する研究に従事.

ものかったいまけ 森川 大輔 2005年, 同志社大学大学院電気工学専 攻修士課程修了. 同年, キヤノン (株) 入社. 複合機の電 気ハード設計に従事. 2009年から, 複合機向けの ASIC 開発に従事. 2021年から, リコー電子デバイス (株)(現 日清紡マイクロデバイス (株)) にてイメージセンサ及び 画像認識の研究に従事.

図 5 特徴量抽出モードにおける構成可変コンパレータ

図 6 画像撮像モード時の A/D 変換特性 (10-bit)

図 7 特徴量抽出モード時の A/D 変換特性 (5-bit)

いる,可変分解能シングルスロープ型 A/D 変換器について 検討した.特徴量抽出モード時において,構成可変コンパ レータは,ピーク電流制限回路を備える CSDA と,帰還制 御を用いたソース接地回路で構成することによって,画像撮

表 1 シミュレーション結果

|      | 画像撮像モード         | 特徴量抽出モード        |

|------|-----------------|-----------------|

| 分解能  | 10-bit          | 5-bit           |

| DNL  | +0.1/-0.0 [LSB] | +0.1/-0.4 [LSB] |

| INL  | +2.5/-1.3 [LSB] | +0.8/-0.6 [LSB] |

| 消費電流 | 14.96 [μA]      | 1.82 [μA]       |

像モード時と比較して,87.83%削減可能なことをSPICEシミュレーションを用いて確認した.今後は提案回路の試作および測定評価を行う予定である.

**謝辞** 本研究は東京大学 VDEC 活動を通して, 日本ケイデンス・デザイン・システムズ社, 日本シノプシス合同会社の協力で行われたものである.

# (文献)

- 1) 神永晉, 金尾寛人: "トリリオン・センサのもたらす変革: 研究開発から 産業創出へ (<特集>トリリオンセンサユニバースにおけるシステム制御情 報技術)", システム/制御/情報, **59**, 11, pp. 400–405 (2015).

- Y. Morikaku, R. Ujiie, D. Morikawa, H. Shima, K. Yoshida and S. Okura: "On-Chip Data Reduction and Object Detection for a Feature-Extractable CMOS Image Sensor", Electronics, 13, 21 (2024).

- K. Itsuki, A. Otani, H. Ogawa and S. Okura: "A Variable-Resolution SAR ADC with 10-bit Image Capturing Mode and 5-bit Feature Extraction Mode", ITE Technical Report, 46, 41, pp. 43–44 (2022).

- K. Kuroda, Y. Morikaku, Y. Osuka, R. Iegaki, K. Yoshida and S. Okura: "Lightweight Object Detection Model for a CMOS Image Sensor with Binary Feature Extraction", 2024 IEEE SENSORS (2024).

- T. Lin, M. Maire, S. Belongie, J. Hays, P. Perona, D. Ramanan,

P. Dollár and C. Zintnick: "Microsoft COCO: Common Objects in Context", Computer Vision – ECCV 2024, pp. 740–755 (2014).

- 6) S. Sukegawa, T. Umebayashi, T. Nakajima, H. Kawanobe, K. Koseki, I. Hirota, T. Haruta, M. Kasai, K. Fukumoto, T. Wakano, K. Inoue, H. Takahashi, T. Nagano, Y. Nitta and N. Fukushima: "A 1/4 inch 8Mpixel Back-Illuminated Stacked CMOS Image Sensor", 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, pp. 484–485 (2013).

- M. Bazes: "Two Novel Fully Complementary Self-Biased CMOS Differential Amplifiers", IEEE Journal of Solid-State Circuits, 26, 2, pp. 165–168 (1991).

This is a machine translated version of the original paper in Japanese (Published on J-STAGE).

The next page is the original paper, which is expanded alternately with the translated version.

Because this is a machine translation, it may contain typographical errors, mistranslations, or parts of the paper that have not been reflected in the translation.

Please be sure to cite the original publication when referencing.

しま **秀樹** 2004 年,大阪大学大学院工学研究科博士後期課程単位取得退学.同年,日本テキサス・インスツルメンツ (株) 入社.電源 IC の開発に従事.2014年から,リコー電子デバイス (株)(現日清紡マイクロデバイス (株)) にて電源 IC の開発,イメージセンサ及び画像認識の研究に従事.博士 (工学).

おおくら しゅんすけ 大倉 俊介 2003年,大阪大学卒業。2005年,同 大学院博士前期課程修了。2010年,同大学院博士(工学) を取得。2019年より立命館大学理工学部電子情報工学 科 准教授。2024年より同大学 教授。CMOS イメージ センサの画素デバイスや周辺回路,ハードウェアセキュ リティ,画像認識,IoT への応用などの研究に従事。正 会員。

おおくら しゅんすけ 大倉 俊介 2003年,大阪大学卒業. 2005年,同 大学院博士前期課程修了. 2010年,同大学院博士(工学) を取得. 2019年より立命館大学理工学部電子情報工学 科 准教授. 2024年より同大学 教授. CMOS イメージ センサの画素デバイスや周辺回路,ハードウェアセキュ リティ,画像認識,IoT への応用などの研究に従事. 正 会員.